Synchronous Transfer

- In this mechanism one of the control lines of the bus carries clock pulses, which provide timing signals to the CPU and the main memory.

- A memory operation can be completed in one cycle

- The synchronous bus scheme leads to simpler implementation, but it can not accommodate devices of widely varying speed

- So the speed of all the devices must be reduced to that of the slowest one

Storing a Word into the Memory

- CPU loads the address in which the content is to be stored in the MAR

- The data to be stored in MDR

- At the same time Write command is issued

- Again here also the CPU carries out the tasks which do not require MAR and MDR when it is waiting for MFC signal

Storing a Word into the Memory

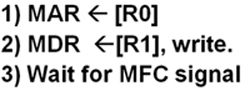

Following sequence illustrates write operation assuming that data to be stored in the memory is in R1 and memory address is in R0.

Fetching a word from the memory << Previous

Next >>Register Transfers

Support us generously: contact@lessons2all.com

Our aim is to provide information to the knowledge seekers.

.jpg)